內容目錄

研究介紹

本實驗室過去對於非晶矽氫a-Si:H材料,從材料的成長到元件的製備已有多年的經驗,可製作具良好元件穩定性的非晶矽薄膜電晶體。本實驗室亦使用微晶矽(microcrystalline silicon, μc-Si)製作TFT元件。微晶矽具有部份結晶性,可以達到更好的元件特性,在製程上亦與a-Si:H類似,因此可同時具備兩者的優點。此外,我們發展出低溫多晶矽製程,利用雷射退火配合週期性金屬結構,可以使多晶矽薄膜電晶體的元件特性具有較佳的均勻度。我們也將研究材料延伸至金屬氧化物,利用摻雜氮元素製作出具有良好特性的氧化鋅薄膜電晶體,並且對於銦鎵鋅氧化物(InGaZnO, IGZO)材料載子濃度的控制機制做了詳細的研究,利用N2O treatment能有效減少IGZO中氧空缺的特性,來製作具有濕蝕刻阻擋層(etching stop layer, ESL)的IGZO TFT元件。

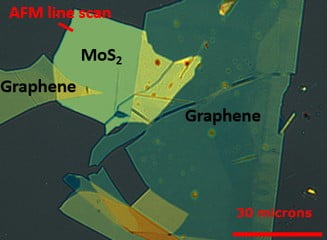

近年來,為了將電晶體元件製作尺寸縮小至奈米等級,以應用在各種微小電子電路的設計製作上,我們將研究延伸至二維材料,利用石墨烯(graphene)和二硫化鉬(MoS2)製作出具有良好電特性的TFT元件。利用二維材料的特性,我們只需要單層或少層的二維材料,即可得到良好的電晶體特性,同時它也能有效降低短通道效應所造成的影響,使元件製作尺寸能夠縮小至奈米級。研究成果如附圖一、二。

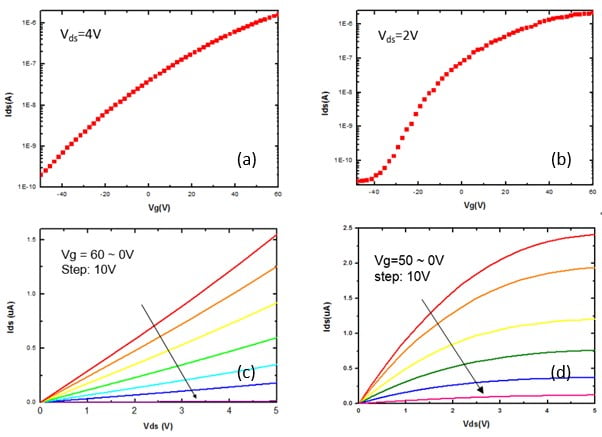

圖二 (a)(c) MoS2 TFT成長氧化鋁保護層之前的電性。

(b)(d) MoS2 TFT成長氧化鋁保護層之後的電性。

研究成果

- 利用化學氣相沉積成長的非晶矽薄膜,製作出非晶矽薄膜電晶體。

- 利用熱燈絲化學氣相沉積法製作出微晶矽薄膜電晶體。

- 利用雷射退火配合週期性金屬結構,製作出高均勻度多晶矽薄膜電晶體元件。

- 利用Atomic Layer Deposition成長之ZnO:N薄膜,製作出具有良好元件電性之金屬氧化物薄膜電晶體。

- 利用二維材料MoS2,graphene作為接觸電極,配合Atomic Layer Deposition成長之Al2O3薄膜作為保護層,製作出具有良好元件電性之MoS2薄膜電晶體。

參考文獻

S. C. Yang, C. H. Cheng, C. Y. Hsueh, S.C. Lee, 2014 “Selective Deposition of High-k Capping Layer on MoS2 Field Effect Transistors by Using Graphene Electrodes” Graphene conference, accepted.